สถาปัตยกรรมเปรียบเสมือนการเล่นแร่แปรธาตุ คือเป็นการรวบรวมทรานซิสเตอร์ที่ดีที่สุดสำหรับเครื่องจักรที่ถูกกำหนด นำมาเชื่อมต่อกันผ่านบรรจุภัณฑ์ที่มีประสิทธิภาพสูง ควบรวมกับแบนด์วิธสูง (high-bandwidth) แคชพลังงานต่ำ (low-power caches) จากนั้นติดตั้งทั้งหมดเข้ากับหน่วยบันทึกความจำความจุสูง และเชื่อมต่อกันด้วยความหน่วงที่ต่ำ เพื่อสร้างคลัสเตอร์การประมวลผลแบบไฮบริดในแพ็คเกจเดียวกัน ในขณะเดียวกัน ก็ต้องแน่ใจว่าซอฟต์แวร์ทั้งหมดจะเร่งความเร็วได้อย่างราบรื่น โดยการเปิดเผยด้านนวัตกรรมทางสถาปัตยกรรมที่เหล่าสถาปนิกของอินเทลได้สร้างสรรค์อย่างต่อเนื่อง เพื่อการปล่อยตัวผลิตภัณฑ์ต่างๆ ในเร็ววันนี้ นับเป็นสิ่งที่พวกเขาตั้งตารอในทุกๆ ปี และในปีนี้ งาน Intel Architecture Day ครั้งที่สามของเรา จะเป็นงานที่น่าตื่นเต้นที่สุดเท่าที่เคยมีมา

วันนี้ อินเทลได้เผยถึงการเปลี่ยนแปลงครั้งใหญ่ที่สุดทางสถาปัตยกรรมในยุคนี้ รวมถึงให้ข้อมูลเกี่ยวกับ Alder Lake โดยละเอียดเป็นครั้งแรก ซึ่งเป็นสถาปัตยกรรมไฮบริดที่มีประสิทธิภาพ (performance hybrid architecture) ตัวแรกของอินเทลที่มาพร้อมกับ คอร์ x86 จำนวน 2 รุ่น และตัวกำหนดเวิร์คโหลดอัจฉริยะอย่าง Intel® Thread Director ร่วมด้วย Sapphire Rapids สถาปัตยกรรมดาต้าเซ็นเตอร์มาตรฐานใหม่ของอินเทล ที่มาพร้อมคอร์ประสิทธิภาพใหม่ และเอ็นจิ้นการเร่งความเร็วที่หลากหลาย นอกจากนี้ อินเทลยังเปิดตัวสถาปัตยกรรมใหม่ด้านหน่วยประมวลผลกราฟิก (GPU) สำหรับเกมที่สามารถแยกส่วนได้ หน่วยประมวลผลโครงสร้างพื้นฐาน (IPU) แบบใหม่ และ Pointe Vecchio สถาปัตยกรรม GPU สำหรับศูนย์ข้อมูลที่มาพร้อมความชำนาญขั้นสูง และความหนาแน่นในการประมวลผลสูงสุดเท่าที่เคยมีมาของอินเทล

ความก้าวหน้าทางสถาปัตยกรรมเหล่านี้ ถือเป็นจุดเริ่มต้นของความเป็นผู้นำด้านผลิตภัณฑ์ในยุคถัดไปของอินเทล ซึ่งจะเริ่มต้นเร็วๆ นี้ ด้วยผลิตภัณฑ์ Alder Lake อย่างไรก็ตาม ความก้าวหน้าต่างๆ ที่เปิดเผยในวันนี้ ยังเป็นการแสดงให้เห็นว่า สถาปัตยกรรมจะสามารถตอบสนองความต้องการด้านการประมวลผลที่มีประสิทธิภาพเพิ่มขึ้นได้อย่างไร เนื่องจากจำนวนเวิร์คโหลดจากเดสก์ท็อปไปยังดาต้าเซ็นเตอร์นั้นมีขนาดใหญ่ขึ้น ซับซ้อนขึ้น และมีความหลากหลายมากกว่าที่เคย

เพิ่มเติม: Intel Architecture Day 2021

สถาปนิกของอินเทลกำลังทำงานอย่างหนักในการผสมผสานหน่วยวัดต่างๆ ทั้ง สเกลาร์, เวกเตอร์, เมทริกซ์ และเอ็นจิ้นการประมวลผลเชิงพื้นที่อันมีเอกลักษณ์ที่โดดเด่นและหลากหลายของอินเทล เพื่อสร้างสถาปัตยกรรมการประมวลผลระบบไฮบริด ที่สามารถมอบผลลัพธ์แบบไม่เป็นเส้นตรง (non-linear) เพื่อรองรับเวิร์คโหลดที่มีความต้องการสูงที่สุดสำหรับลูกค้าของเรา

หากสนใจท่านสามารถเข้าไปอ่านข่าวประชาสัมพันธ์ และรับชมวิดีโอเพิ่มเติมได้ที่เว็บไซต์ Intel Newsroom อย่างไรก็ตาม สาระสำคัญหลักที่เราได้ประกาศไป มีดังนี้

คอร์ x86 เต็มประสิทธิภาพ (Efficient): x86 มาพร้อมกับสถาปัตยกรรมไมโคร (microarchitecture) ที่สามารถปรับความยืดหยุ่นได้ เพื่อตอบสนองความต้องการด้านการประมวลผลในทุกช่วงความต้องการของลูกค้า ตั้งแต่แอปพลิเคชันบนโทรศัพท์มือถือที่ใช้พลังงานต่ำ ไปจนถึงสถาปัตยกรรมซอฟต์แวร์ไมโครเซอร์วิส (microservices) ที่มีหลายคอร์ เมื่อเทียบกับ Skylake ซึ่งเป็นซีพียูสถาปัตยกรรมไมโครที่มีประสิทธิภาพมากที่สุดของอินเทล จะเห็นได้ว่า คอร์ Efficient สามารถมอบประสิทธิภาพได้มากกว่า 40% ที่กำลังไฟเท่าเดิม หรือมอบประสิทธิภาพเท่าเดิมในขณะที่กินไฟน้อยกว่าถึง 40%1 สำหรับประสิทธิภาพด้านปริมาณงาน คอร์ Efficient สี่คอร์สามารถมอบประสิทธิภาพการทำงานเพิ่มขึ้น 80% ในขณะที่ยังคงใช้พลังงานน้อยกว่าคอร์ Skylake สองคอร์ที่รันสี่เธรด หรือประสิทธิภาพด้านปริมาณงานเท่ากันในขณะที่ใช้พลังงานน้อยกว่าถึง 80%1

คอร์ x86 เต็มสมรรถภาพ (Performance): นอกจากจะเป็นคอร์ซีพียูที่มีประสิทธิภาพสูงสุดที่อินเทลเคยสร้างมาแล้ว คอร์ x86 ยังมอบฟังก์ชันขั้นบันได (step function) ในประสิทธิภาพของสถาปัตยกรรมซีพียู ที่จะขับเคลื่อนการประมวลผลไปได้ถึงทศวรรษหน้า โดยคอร์ดังกล่าว ได้รับการออกแบบให้เป็นสถาปัตยกรรมที่กว้างกว่า ลึกกว่า และชาญฉลาดกว่า เพื่อให้สามารถมองเห็นการทำงานแบบขนาน (parallelism) ได้มากขึ้น เพิ่มประสิทธิภาพในการดำเนินการแบบขนานได้มากขึ้น ลดความล่าช้าในการส่งข้อมูล และเพิ่มประสิทธิภาพการทำงานโดยรวม นอกจากนี้ยังช่วยสนับสนุนข้อมูลและแอปพลิเคชันที่มีการใช้โค้ดขนาดใหญ่ ทั้งนี้ คอร์ Performance ยังมีการปรับการใช้งานฟังก์ชัน Geomean ได้ดีขึ้นถึง 19% สำหรับเวิร์คโหลดที่หลากหลาย ซึ่งถือว่าทำได้มากกว่าสถาปัตยกรรมอินเทล® คอร์™ เจนเนอเรชั่นที่ 11 (คอร์ Cypress Cove) ที่ความถี่เดียวกัน1

=ด้วยเป้าหมายเพื่อโปรเซสเซอร์ดาต้าเซ็นเตอร์และเพื่อรองรับแนวโน้มการพัฒนาในด้าน machine learning คอร์ Performance นำเสนอฮาร์ดแวร์เฉพาะ ซึ่งรวมถึง Advanced Matrix Extensions (AMX) ใหม่ของอินเทล เพื่อดำเนินการคูณเมทริกซ์สู่ประสิทธิภาพในการดำเนินงานสูงสุด นั่นคือการเพิ่มอัตราการเร่งปัญญาประดิษฐ์ขึ้นสูงถึงเกือบ 8 เท่า1 นอกจากนี้ คอร์ดังกล่าวยังถูกออกแบบมาเพื่อให้ซอฟต์แวร์ใช้งานง่าย โดยใช้ประโยชน์จากโมเดลการเขียนโปรแกรมได้มากถึง 86 เท่า

Intel Thread Director: เครื่องมือพิเศษเฉพาะของอินเทลในการจัดเรียงเวิร์คโหลดต่างๆ ซึ่งถูกพัฒนาขึ้นเพื่อให้แน่ใจว่า คอร์ Efficient และ คอร์ Performance สามารถทำงานร่วมกันได้อย่างราบรื่น โดยการกำหนดเวิร์คโหลดอย่างทรงพลังและชาญฉลาดตั้งแต่เริ่มต้น พร้อมทั้งเพิ่มประสิทธิภาพให้กับระบบเพื่อสมรรถภาพและประสิทธิภาพการดำเนินงานขั้นสูงสุดในโลกการใช้งานจริง ด้วยความชาญฉลาดที่ถูกสร้างขึ้นโดยตรงภายในคอร์ ทำให้สามารถทำงานได้อย่างราบรื่นร่วมกับระบบปฏิบัติการ เพื่อวางเธรดที่ถูกต้อง บนคอร์ที่ถูกต้อง ในเวลาที่ถูกต้อง

Alder Lake: นำเสนอรูปแบบใหม่ของสถาปัตยกรรมมัลติคอร์ Alder Lake จะเป็นสถาปัตยกรรมไฮบริดที่มีประสิทธิภาพ (performance hybrid architecture) ตัวแรกของอินเทล มาพร้อมกับ Intel Thread Director ใหม่ล่าสุด นี่คือสถาปัตยกรรม system-on-chip (SoC) สำหรับผู้ใช้งานที่ชาญฉลาดที่สุดของอินเทล มีการผสมผสานระหว่างคอร์ Efficient และคอร์ Performance ที่สามารถปรับความยืดหยุ่นได้เพื่อการใช้งานตั้งแต่ระดับคอมพิวเตอร์ส่วนบุคคล Ultra-Mobile ไปจนถึงระดับเดสก์ท็อป พร้อมทั้งเป็นผู้นำการเปลี่ยนแปลงในอุตสาหกรรมด้วย I/O และหน่วยความจำชั้นนำของอุตสาหกรรม ทั้งนี้ผลิตภัณฑ์ต่างๆ ที่ใช้ Alder Lake จะเริ่มถูกจัดส่งเพื่อวางจำหน่ายภายในปีนี้

Xe HPG และ Alchemist SoC: สถาปัตยกรรม graphics microarchitecture ถูกออกแบบมาเพื่อปรับความยืดหยุ่นให้เหมาะกับระดับประสิทธิภาพสำหรับเวิร์คโหลดของผู้ที่ชื่นชอบการเล่นเกม และการสร้างสรรค์ผลงานต่างๆ โดยสถาปัตยกรรมไมโครกราฟิก Xe HPG มีคุณสมบัติ Xe- core แบบใหม่ ซึ่งเน้นการประมวลผล รวมทั้งสามารถตั้งโปรแกรมและปรับขนาดได้ พร้อมรองรับ DirectX 12 Ultimate อย่างเต็มรูปแบบ นอกจากนี้ Matrix Engines แบบใหม่ ภายใน Xe-cores (เรียกว่า XMX – Xe Matrix eXtensions) สามารถช่วยเร่งเวิร์คโหลด AI ได้ เช่น XeSS เทคโนโลยีการอัปสเกลแบบใหม่ที่ช่วยให้สามารถเล่นเกมได้อย่างมีประสิทธิภาพ และมีความถูกต้องแม่นยำสูง โดย Alchemist SoC ที่ใช้ Xe HPG (เดิมชื่อรหัส DG2) จะออกวางจำหน่ายในช่วงไตรมาสที่ 1 ปีพ.ศ. 2565 ภายใต้แบรนด์ใหม่ชื่อ Intel® Arc™

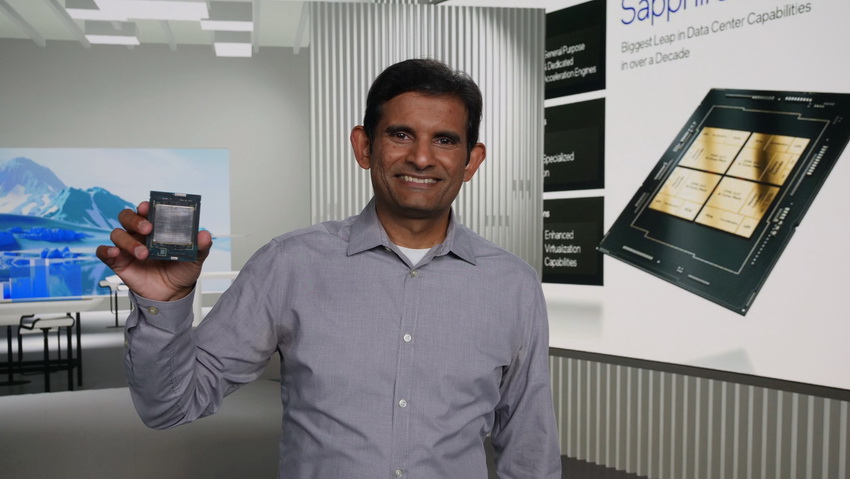

Sapphire Rapids: การกำหนดมาตรฐานสำหรับโปรเซสเซอร์ดาต้าเซ็นเตอร์รุ่นต่อไป เป็นการรวมคอร์ประสิทธิภาพของ Intel เข้ากับคอร์ตัวเร่งความเร็วใหม่ โดยหัวใจหลักของ Sapphire Rapids คือสถาปัตยกรรม SoC แบบเรียงต่อกัน ช่วยมอบความสามารถในการปรับขนาดได้เป็นอย่างดี ขณะที่ยังคงรักษาประโยชน์ของอินเทอร์เฟสซีพียูแบบเสาหิน (monolithic CPU interface) ด้วยเทคโนโลยีบรรจุภัณฑ์ EMIB (Embedded Multi-die Interconnect Bridge) ของอินเทล และสถาปัตยกรรมแบบ mesh ขั้นสูง

Infrastructure Processing Unit: อินเทลได้เปิดตัว IPU ที่ใช้ ASIC โดยเฉพาะตัวแรกภายใต้ชื่อรหัส Mount Evans พร้อมกับแพลตฟอร์มอ้างอิง IPU ที่ใช้ FPGA ตัวใหม่คือ Oak Springs Canyon ด้วยสถาปัตยกรรมที่ใช้ Intel IPU ผู้ให้บริการระบบคลาวด์ (CSPs) สามารถเพิ่มรายได้จากดาต้าเซ็นเตอร์ให้สูงสุด โดยการลดภาระงานด้านโครงสร้างพื้นฐานจาก CPU ไปยัง IPU นอกจากนี้ การถ่ายโอนงานด้านโครงสร้างพื้นฐานไปยัง IPU ยังช่วยให้ CSPs สามารถปล่อยเช่า ซีพียู เซิร์ฟเวอร์ต่างๆ ให้กับลูกค้าได้ 100 เปอร์เซ็นต์

Xe HPC Ponte Vecchio: นวัตกรรม SoC ที่ซับซ้อนที่สุดตั้งแต่อินเทลเคยผลิตมา สะท้อนให้เห็นถึงเป้าหมายของอินเทลที่ต้องการจะปลุกแผนกลยุทธ์ IMD 2.0 ให้มีชีวิต โดย Ponte Vecchio เป็นผลผลิตจากกระบวนการผลิตเซมิคอนดักเตอร์ (semiconductor) ที่ล้ำสมัย มีเทคโนโลยีการเชื่อมต่อแบบ EMIB multi-die และรูปแบบบรรจุภัณฑ์สามมิติแบบ Foveros 3D อินเทลกำลังเดินหน้าทำโปรเจ็กต์ที่ยิ่งใหญ่ เพื่อจะผลิตอุปกรณ์ทรานซิสเตอร์กว่า 1 แสนล้านตัว ที่มอบหน่วยวัดความเร็วแบบการปฏิบัติการจุดลอยตัวต่อวินาที (FLOPs) ที่ล้ำหน้าที่สุดในอุตสาหกรรม รวมถึงมอบความหนาแน่นในการประมวลผล เพื่อเร่งการทำงานของปัญญาประดิษฐ์ (Artificial Intelligence - AI), คอมพิวเตอร์ประสิทธิภาพสูง (High Performance Computing – HPC) และการวิเคราะห์เวิร์คโหลดขั้นสูง ณ งาน Architecture Day อินเทลได้เผยให้เห็นถึงประสิทธิภาพความเป็นผู้นำผ่านซิลิกอน Ponte Vecchio รุ่นแรกของอินเทล โดยสร้างสถิติอุตสาหกรรมทั้งในการอนุมานและปริมาณงานด้านการฝึกอบรมบนเกณฑ์มาตรฐาน AI ที่ได้รับความนิยม1 นอกจากนี้ อินเทลได้เปิดเผยว่า ซิลิกอน A0 ให้ผลลัพธ์ปริมาณงานได้มากกว่า 45 TFLOPS FP32, ประสิทธิภาพการทำงานของเมมโมรี่ แฟบริค แบนด์วิธ (Memory Fabric bandwidth) มากกว่า 5-TBps และแบนด์วิธการเชื่อมต่อที่มากกว่า 2 TBps เช่นเดียวกับสถาปัตยกรรม Xe ทั้งนี้ Ponte Vecchio จะเปิดใช้งานด้วย oneAPI ซึ่งเป็นสแต็คซอฟต์แวร์รวมศูนย์แบบเปิด ข้ามผู้จำหน่าย ข้ามสถาปัตยกรรม และเป็นไปตามมาตรฐานของเรา

ในปีที่ผ่านมา เทคโนโลยีเป็นหัวใจสำคัญของการสื่อสาร การทำงาน การรับความบันเทิง และการเอาชีวิตรอดท่ามกลางสถานการณ์การแพร่ระบาดของเชื้อไวรัสโควิด-19 ระบบคอมพิวเตอร์ที่ทรงพลังได้พิสูจน์แล้วว่าเป็นสิ่งที่จำเป็นอย่างมากในยุคนี้ เมื่อมองต่อไปในอนาคต เราจะเห็นถึงความต้องการด้านการประมวลผลเพิ่มขึ้นเป็นอย่างมาก ประมาณค่าต้องการได้สูงถึง 1,000 เท่า ภายในปีพ.ศ. 2568 การเพิ่มขึ้นกว่าหนึ่งพันเท่าตัวภายในสี่ปีนั้นเป็นไปตามกฎของมัวร์ (Moore’s Law) ของพลังทั้งห้าอย่าง (the power of five)

ประธานคณะผู้บริหารของอินเทล นายแพท เกลซิงเกอร์ ในฐานะสถาปนิกของอินเทล ได้กล่าวที่งาน Architecture Day ว่า “พวกเรากำลังเผชิญหน้ากับความท้าทายทางด้านการประมวลผล ซึ่งสามารถถูกแก้ได้ผ่านสถาปัตยกรรมและแพลทฟอร์มที่ล้ำสมัย สถาปนิกและวิศวกรที่ชำนาญการของเราสามารถสรรสร้างเทคโนโลยีเหล่านี้ให้กลายเป็นจริงได้”

ขณะนี้ โลกของเรากำลังพึ่งพาเหล่าบรรดาวิศวกรและสถาปนิกที่พยายามแก้ปัญหาทางด้านคอมพิวเตอร์ที่ซับซ้อนที่สุด เพื่อพัฒนาคุณภาพการใช้ชีวิตของผู้คนให้ดียิ่งขึ้น นี่จึงเป็นเหตุผลให้กลยุทธ์และการดำเนินการของอินเทลกำลังถูกเร่งความเร็วเพื่อตอบสนองความต้องการเหล่านี้อย่างรวดเร็ว

หมายเหตุ : 1 สำหรับข้อมูลเกี่ยวกับเวิร์คโหลดและการกำหนดค่าต่างๆ สามารถเข้าไปเยี่ยมชมได้ที่: www.intel.com/ArchDay21claims

บทความโดย : นายราชา โคดาริ